# UVVM

## The main benefits of the world's #1 VHDL Verification Methodology

By Espen Tallaksen, Director FPGA and Space, EmLogic

## EmLogic

The Norwegian Embedded Systems & FPGA Design Centre

## Agenda

- Introduction

- The basics of UVVM for simple testbenches

- The basics of UVVM for advanced testbenches

- The main benefits of UVVM

- Why UVVM is better

## What is UVVM?

- Number 1 world-wide for VHDL verification \*1

- By far the fastest growing (indep. of lang.) \*1

- Very structured infrastructure and architecture

Simplicity where it matters the most

- $\rightarrow$  Significantly improves Verification Efficiency

- $\rightarrow$  Assures a far better Design Quality

- $\rightarrow$  Unique Reuse friendliness

- Extremely fast adoption by the world-wide VHDL community

- Recommended by Doulos for Testbench architecture

- Supported by more and more EDA vendors

- ESA projects to extend the functionality

FPGA ASIC CPLD

### Simple as default Advanced when needed

\*1: According to The Wilson Research Group Functional Verification Study from September 2020

## The full overview...

... is not possible to give in this short presentation, but...

- You can find significantly more details in my previous free webinars for Mentor/Siemens and Trias:

- 1. An introduction to efficient VHDL verification using the open source UVVM https://trias-mikro.de/webinars/an-introduction-to-efficient-vhdl-verification-using-the-open-source-uvvm/

- 2. UVVM Advanced VHDL Verification Made simple https://trias-mikro.de/webinars/uvvm-advanced-vhdl-verification-made-easy/

- 3. Modern VHDL testbenches.

*An AXI4-stream example, First dead simple, then advanced – as simple as possible* <u>https://trias-mikro.de/webinars/modern-vhdl-testbenches-an-axi-stream-example-first-dead-simple-then-advanced-as-simple-as-possible/</u>

- I can send you a PDF of the presentations on request (espen.tallaksen@emlogic.no)

- Above webinar references is used in some of the following slides. See webinar ?

# The basics of UVVM - For simple testbenches

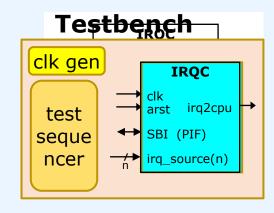

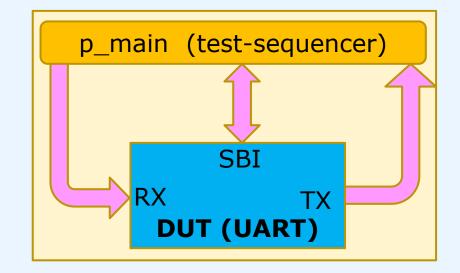

### Typical simple verif. scenario - a low complexity interrupt controller

clock\_generator(clk, GC\_CLK\_PERIOD);

#### All procedures with:

- Positive acknowledge If wanted

- Alert message and mismatch report

- Alert count and ctrl

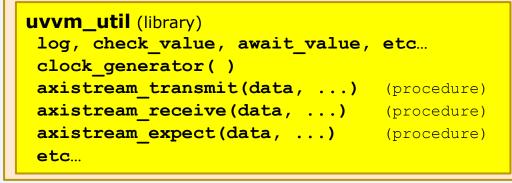

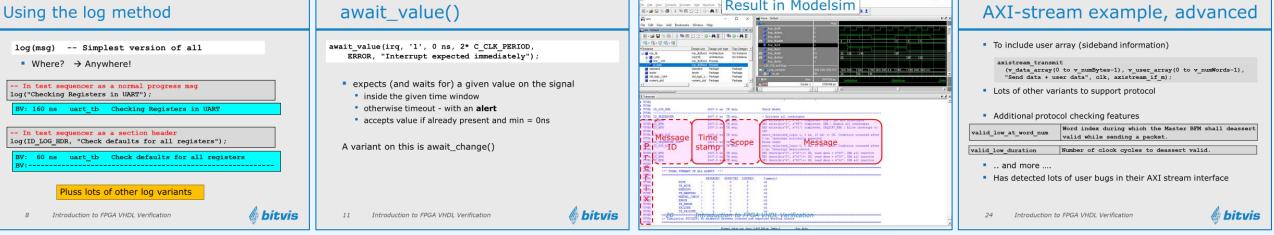

## More in UVVM Utility Library

- check\_stable(), await\_stable()

- clock\_generator(), adjustable\_clock\_generator()

- random(), randomize()

- gen\_pulse()

- block\_flag(), unblock\_flag(), await\_unblock\_flag()

- await\_barrier()

- enable\_log\_msg(), disable\_log\_msg()

- to\_string(), fill\_string(), to\_upper(), replace(), etc...

- normalize\_and\_check()

- set\_log\_file\_name(), set\_alert\_file\_name()

- wait\_until\_given\_time\_after\_rising\_edge()

• etc...

## Well Documented

### UVVM Utility Library – Quick Reference

| Checks and awaits                                                                              | String handling                                                                   |

|------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| <pre>[v_bool :=] check_value(value, [exp], alert_level, msg, [])</pre>                         | v_string := to_string(val, [])                                                    |

| <pre>[v_bool :=] check_value_in_range(value, min_value, max_value, alert_level, msg, [])</pre> | v_string := justify(val, justified, width, format_spaces, truncate)               |

|                                                                                                | v_string := fill_string(val, width)                                               |

| check_stable(target, stable_req, alert_level, msg, [])                                         | v_string := to_upper(val)                                                         |

| await_change(target, min_time, max_time, alert_level, msg, [])                                 | <pre>v_character := ascii_to_char(ascii_pos, [ascii_allow])</pre>                 |

| await_value(target, exp, min_time, max_time, alert_level, msg, [])                             | v_int := char_to_ascii(character)                                                 |

| await_stable(target, stable_req, stable_req_from, timeout, timeout_from, alert_level, msg, []) | <pre>v_natural := pos_of_leftmost(character, string, [result_if_not_found])</pre> |

|                                                                                                | v natural := pos of rightmost(character, string, [result if not found])           |

#### 1.1 Checks and awaits

|                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | • |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Name                         | Parameters and examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |

| [v_bool :=]<br>check_value() | <pre>val(bool), [exp(bool)], alert_level, msg, [scope, [msg_id, [msg_id_panel]]] val(sl), exp(sl), [match_strictness], alert_level, msg, [scope, [msg_id, [msg_id_panel]]] val(sl), exp(slv), [match_strictness], alert_level, msg, [scope, [radix, [format, [msg_id, [msg_id_panel]]]]) val(u), exp(u), alert_level, msg, [scope, [radix, [format, [msg_id, [msg_id_panel]]]]) val(s), exp(s), alert_level, msg, [scope, [radix, [format, [msg_id, [msg_id_panel]]]]) val(int), exp(int), alert_level, msg, [scope, [msg_id, [msg_id_panel]]] val(real), exp(real), alert_level, msg, [scope, [msg_id, [msg_id_panel]]] val(time), exp(time), alert_level, msg, [scope, [msg_id, [msg_id_panel]]] Examples check_value(v_int_a, 42, WARNING, "Checking the integer"); v_check := check_value(v_slv5_a, "11100", MATCH_EXACT, ERROR, "Checking the SLV", "My Scope",</pre> | Checks if val equals exp, and alerts with severity alert_level if the<br>values do not match.<br>The result of the check is returned as a boolean if the method is<br>called as a function.<br>If val is of type slv, unsigned or signed, there are additional optional<br>arguments:<br>- match_strictness: Specifies if match needs to be exact or std_match<br>, e.g. 'H' = '1'. (MATCH_EXACT, MATCH_STD)<br>- radix : for the vector representation in the log: BIN, HEX, DEC or<br>HEX_BIN_IF_INVALID.<br>(HEX_BIN_IF_INVALID means hexadecimal, unless there are the<br>vector contains any<br>U, X, Z or W, - in which case it is also logged in binary radix.)<br>- format may be AS_IS or SKIP_LEADING_0. Controls how the vector<br>is formatted in the log. |   |

| [tb_]error(msg, [scope]      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |

| [tb_]failure(msg, [scope]    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Signal generators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |

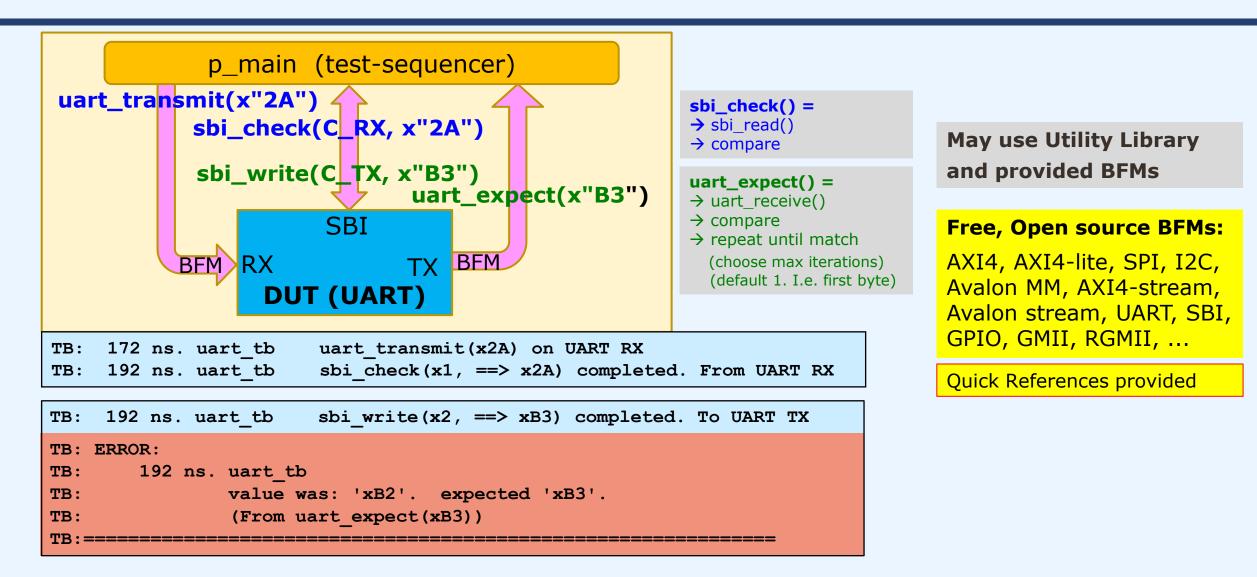

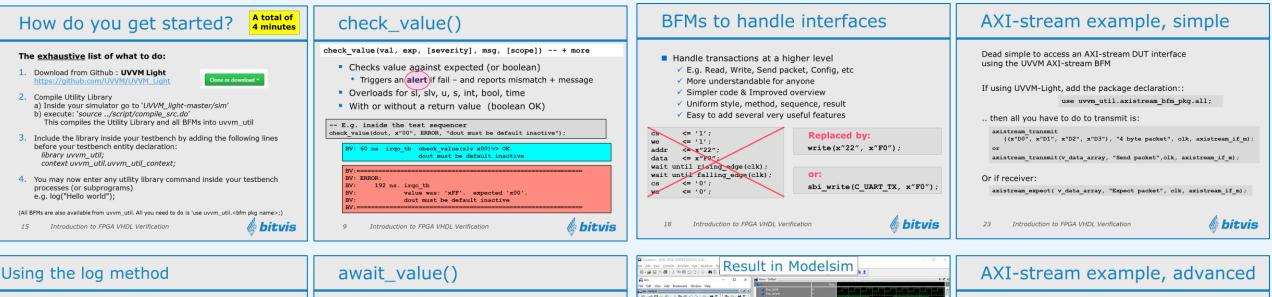

## Simple data communication

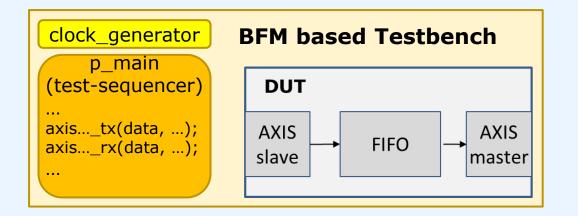

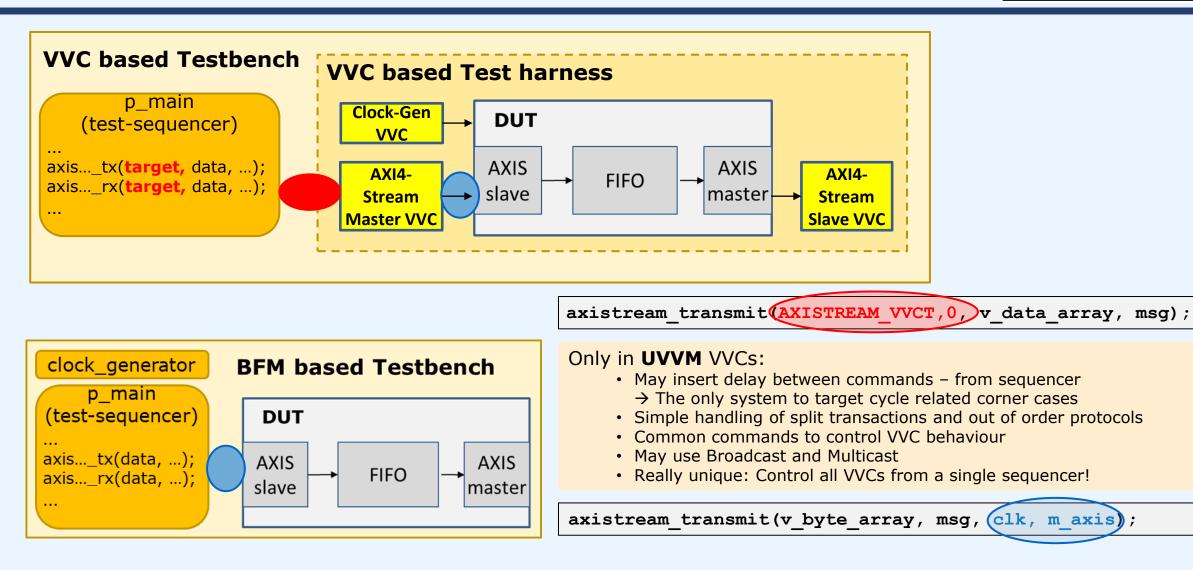

## AXI-stream BFM based TB

### - as simple as possible

### UVVM\_Light (from github)

axistream\_transmit(v\_byte\_array, msg, clk, m\_axis);

- No test harness (for simplicity)

- Sequencer has direct access to DUT signals

- Thus BFMs from p\_main can also see the DUT signals

Only need to download from Github (clone or zip) and compile (total 5 min)

- Simplified UVVM

- For simple usage

- Subset of UVVM No VVCs or VCC support

- All BFMs in the same directory and library

## More details on Intro to UVVM

Page 11 UVVM - The main benefits of ....

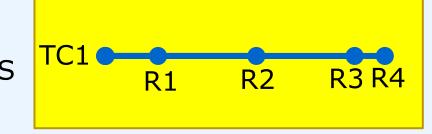

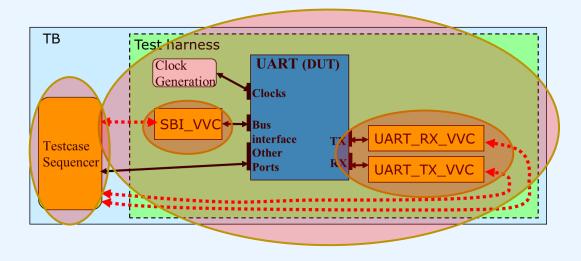

# The basics of UVVM - For advanced verification

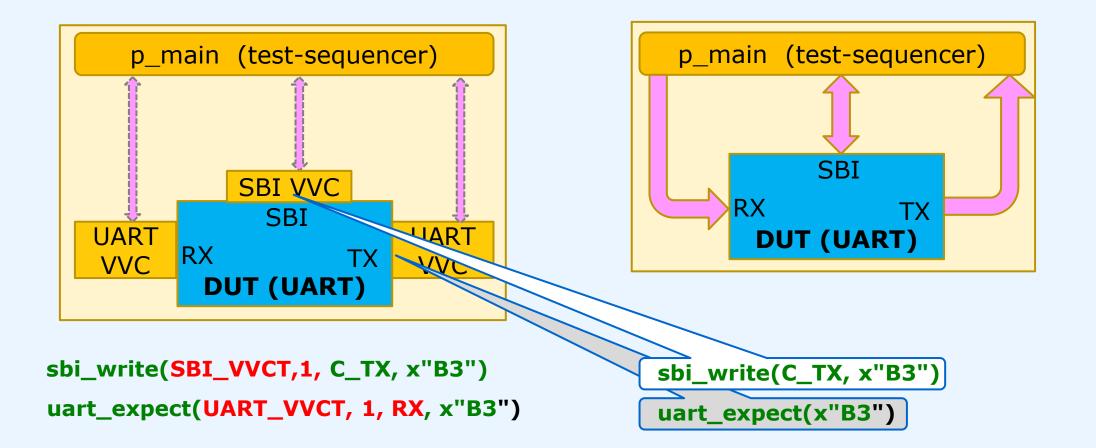

## BFM to VVC: Why and how?

- BFMs are great for simple testbenches

- Dedicated procedures in a simple package

- Just reference and call from a process

- BUT

- A process can only do one thing at a time

- Either execute that BFM

- Or execute another BFM

- Or do something else

- To do more than one thing:

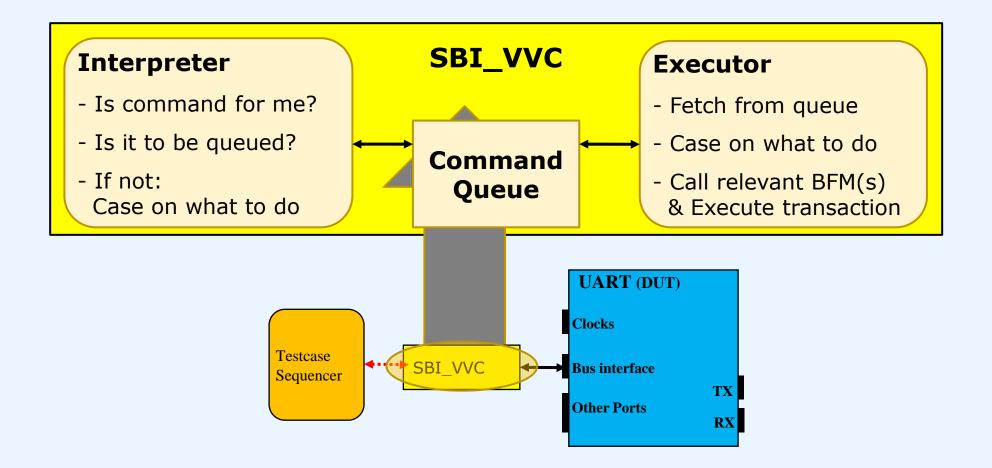

→ Need an entity (or component) (VVC = VHDL Verification Component)

sbi\_write(C\_TX, x"B3")

uart\_expect(x"B3")

## BFM to VVC: Why and how?

## VVC: VHDL Verification Component

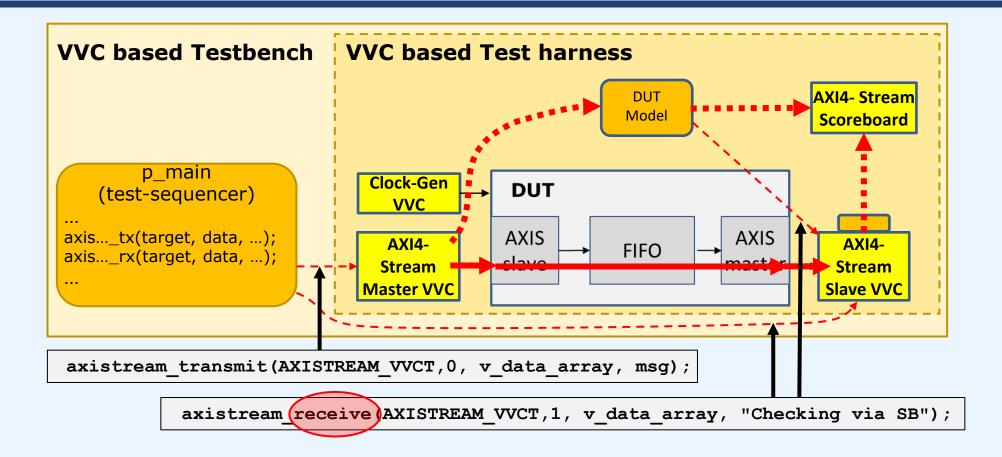

## AXI-stream VVC based TB

### See webinar 3

## Advanced scoreboard-based TB

## **Specification Coverage**

- Assure that all requirements have been verified

- 1. Specify all requirements

- 2. Report coverage from test sequencer (or other TB parts)

- **3.** Generate summary report

- Solutions exist to report that a testcase finished successfully

- BUT reporting that a testcase has finished is not sufficient

- What if multiple requirements are covered by the same testcase?

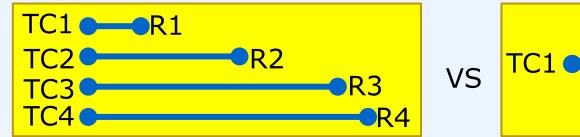

- E.g. Moving/turning something to a to a given position R1: Acceleration R2: Speed R3: Deceleration 4: Position etc..

| Requirement<br>Label | Description                     |

|----------------------|---------------------------------|

| MOTOR_R1             | The acceleration shall be ***   |

| MOTOR_R2             | The speed shall be given by *** |

| MOTOR_R3             | The deceleration shall be ***   |

| MOTOR_R4             | The final position shall be *** |

## More details on – Advanced TBs

### See webinar 3

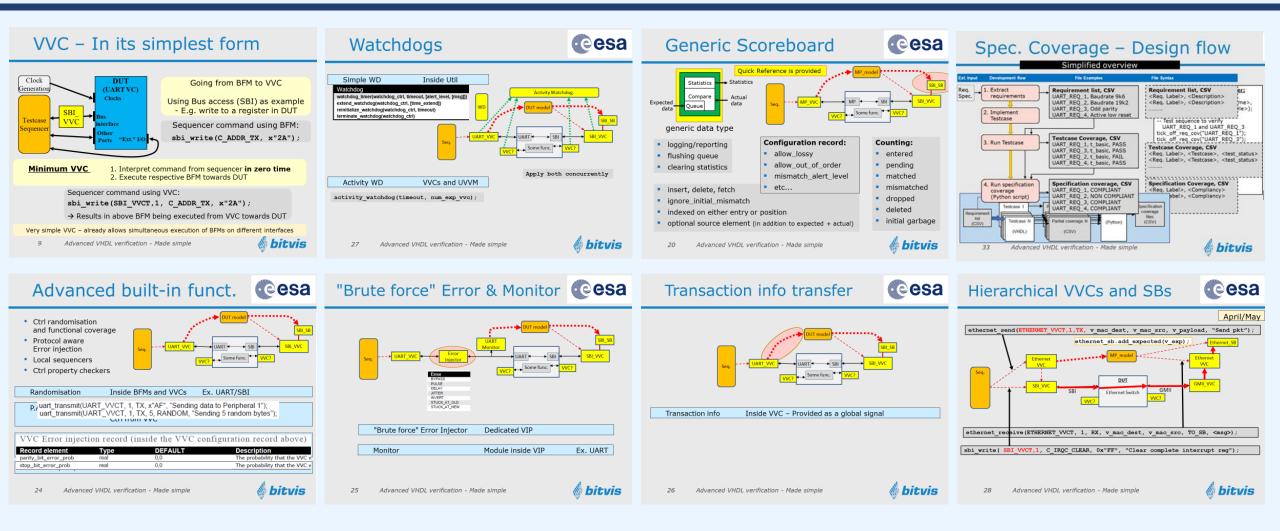

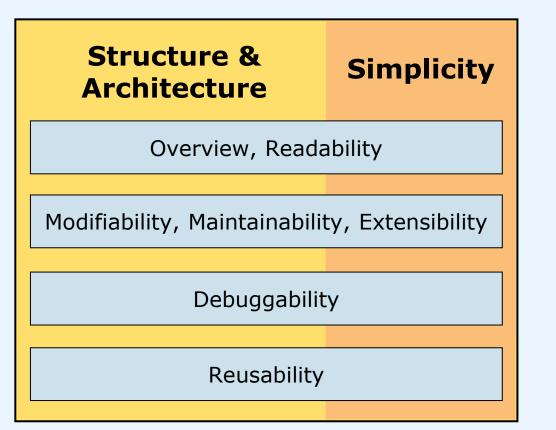

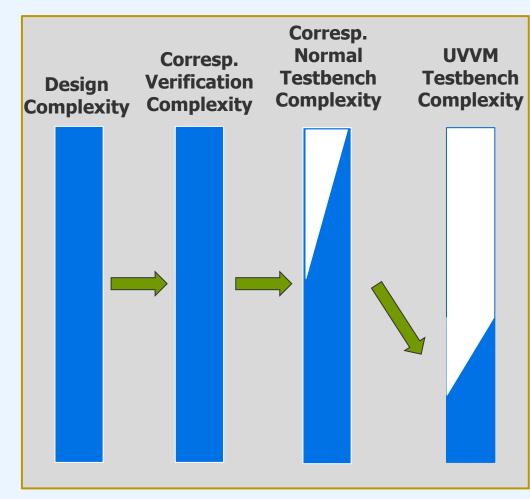

## Main Benefits of UVVM

## Quality and Efficiency enablers

The «mandatory» target for any good Design and Testbench...

# The three main development areas for adv. TBs vs structure and efficiency evaluations

#### The central sequencer

- Always by far the most time consuming

- Massively simplified (commands + sync)

- Even a SW designer can read and write it

- Any number of VVCs easily controlled

- Huge time saving where it matters the most

### Next: Let's check out the reuse potential

#### Test harness

- Dead simple

- Anyone can understand it

- Anyone can understand the interaction

### **Verification Components**

- Autonomous operation

- Encapsulated interface functionality

- Easy to extend with new functionality

- Easy to adapt to more complex protocols

- Plug and play for reuse

- Allows really simple test harness

- Yields a huge improvement for testcase writers

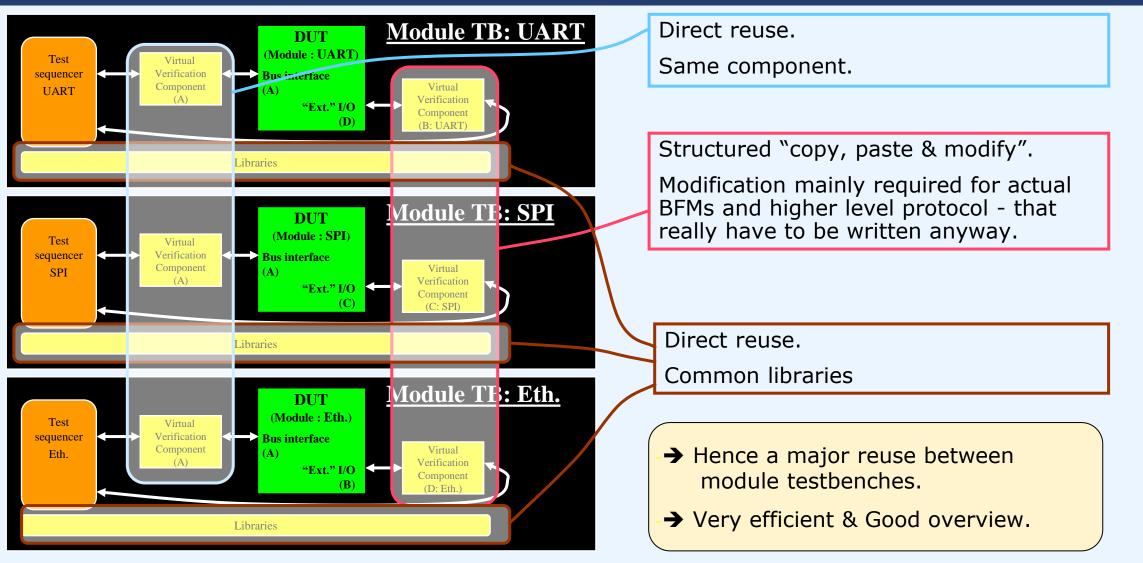

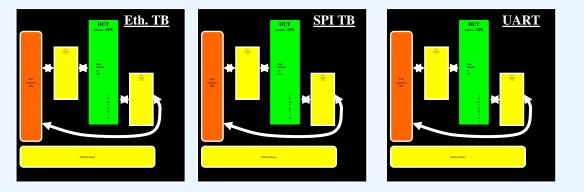

## Reuse between Module Testbences

EmLogic **SIEMENS**

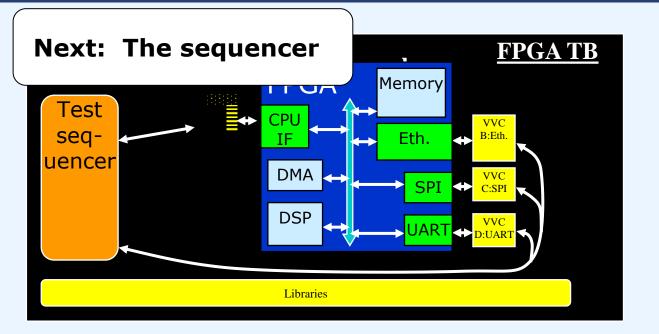

## Reuse from module TBs to FPGA TB

### Work involved for FPGA TB:

- Consider Test harness.

- Remove DUT

- The libraries exist

- - I/O VVCs used as is

- CPU VVC ≈ BUS IF VVC

- Same Command

- Same arch./structure

- Slightly different BFM

- ➔ An extreme reuse from module TBs to FPGA TB

- → Hence FPGA testbench can be made very fast

- → Very efficient & Good overview.

### **Testbench Sequencer**

### Simple example:

sbi\_write(SBI\_VVCT,1 , x"C2", x"58", "Uart TX");

uart\_expect(UART\_VVCT,1,RX, x"58"); uart\_transmit(UART\_VVCT,1,TX, x"A1");

insert\_delay(UART\_VVCT,1,TX, 2\*C\_BIT\_PERIOD); uart\_transmit(UART\_VVCT,1,TX, x"B2"); await completion(UART\_VVCT,1,TX);

sbi\_check(SBI\_VVCT,1, x"C3", x"A1", "Uart RX");

sbi\_check(SBI\_VVCT,1, x"C3", x"B2", "Uart RX");

report\_simulation\_summary;

➔ Anyone can understand it

→ Anyone can write it

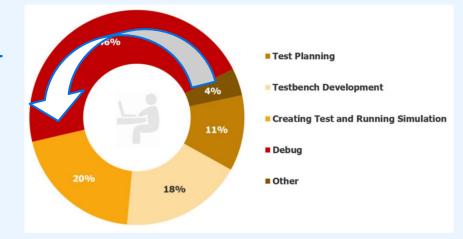

## A huge majority of verification time is spent on:

- -- Writing test cases

- -- Debugging test cases

- -- Adapting a chaotic testbench

- -- Debugging inter process comm.

- Significant speed-up

## Quality and Efficiency enablers - revisited

UVVM provides this. UVVM promotes and encourages this. UVVM facilitates this for your TB UVVM drives your TB towards this

Reusability

Page 26 UVVM - The main benefits of ....

# Why UVVM is better

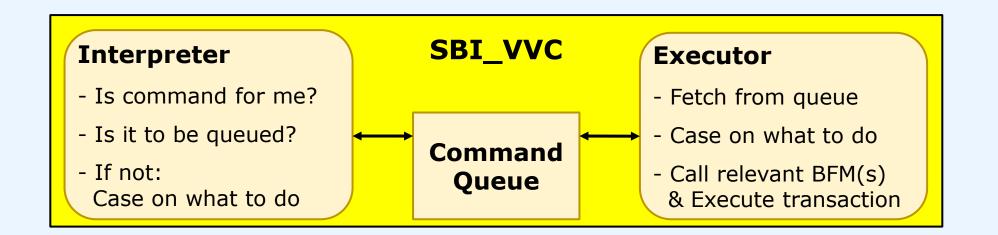

## VVC: VHDL Verification Component

### Same main architecture in every VVC

>95% same code - apart from BFM calls

→ Standard VVC internal architecture

→ Standard VVC external interface

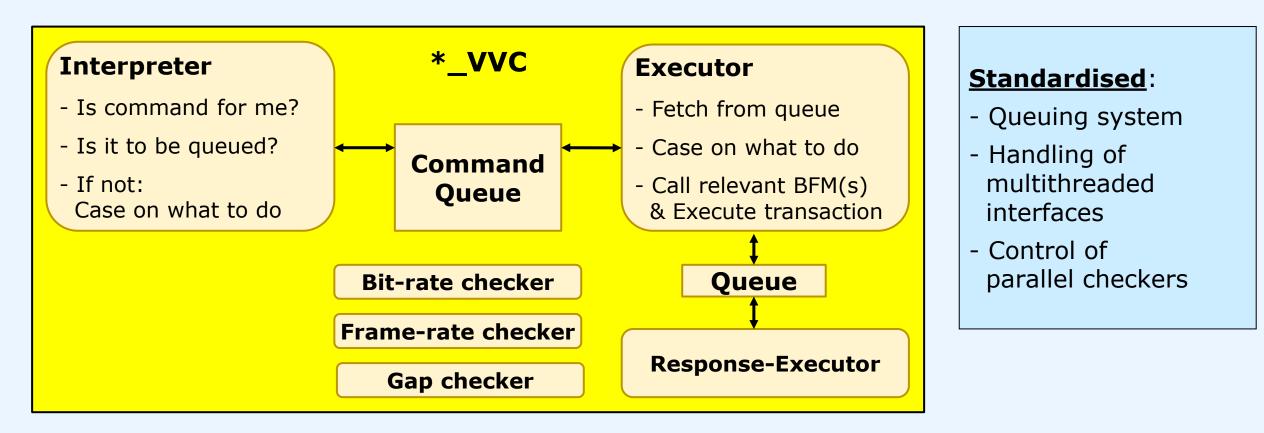

## VVC: Easy to extend

- Easy to add local sequencers

- Easy to add checkers/monitors/etc

- Easy to handle split transactions

- Easy to handle out of order execution

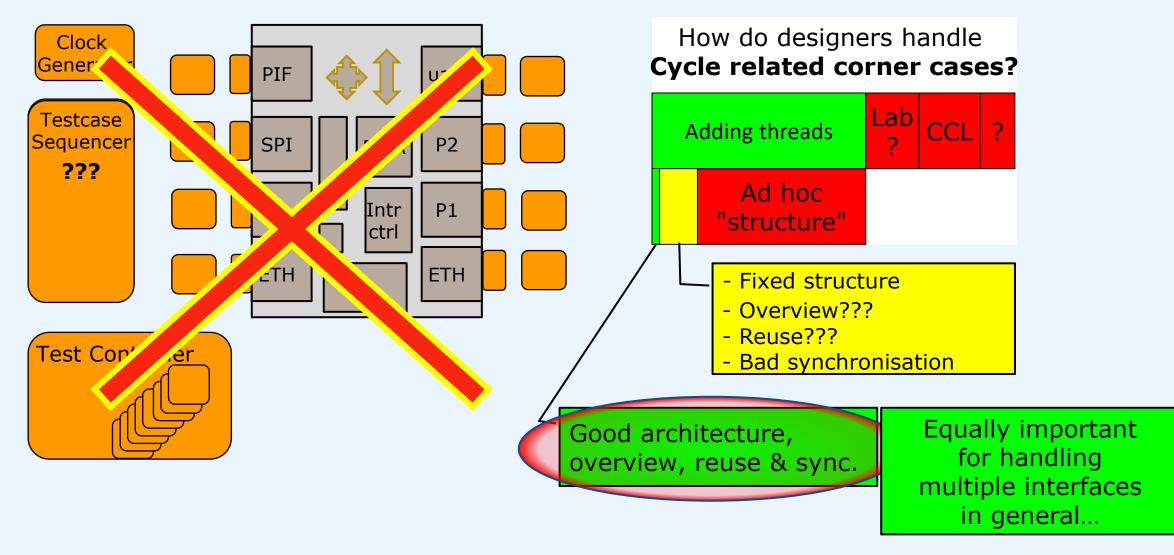

## Cycle related corner cases & Multiple interfaces

## More features unique to UVVM

- May simultaneously control all VVCs from a single sequencer if you like

- Simple synchronization of interface actions from that single sequencer

- May insert delay between commands from sequencer

- Simple handling of split transactions and out of order protocols

- Common commands to control general VVC behaviour

- May use Broadcast and Multicast for common commands

The only system to also target cycle related corner cases

The only system to align all interface stimuli and checks from a single test sequencer process (but still allows multiple test sequencers when that is needed)

## Wishful thinking? - And the result of that

### Wouldn't it be nice if we could ...

$\checkmark$

$\checkmark$

- handle any number of interfaces in a structured manner?

- reuse major TB elements between module TBs?

- reuse major module TB elements in the FPGA TB?

- read the test sequencer almost as simple pseudo code?

- recognise the verification spec. in the test sequencer?

- understand the sequence of event

- just from looking at the test sequencer

## The largest collection of interface models

**UVVM** has by far the largest collection of open source VIP available

All available as both BFMs and VVCs – your choice

| Free, Open source BFMs and VVC (*:VVC-only): |        |                      |  |  |

|----------------------------------------------|--------|----------------------|--|--|

| - AXI4-lite                                  | - SPI  | - GMII               |  |  |

| - AXI4-stream                                | - I2C  | - RGMII              |  |  |

| - Full AXI4                                  | - UART | Ethernet (*)         |  |  |

| - Avalon MM                                  | - GPIO | - Clock Generator    |  |  |

| - Avalon Stream                              | - SBI  | - Error Injector (*) |  |  |

### Summary

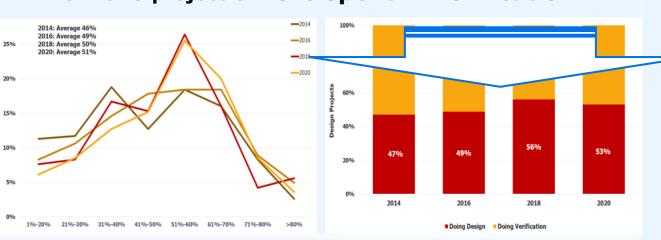

#### Half the project time is spent in verification

#### Half the verification time is spent on debugging

2020 WILSON RESEARCH GROUP, FUNCTIONAL VERIFICATION STUDY, FPGA FUNCTIONAL VERIFICATION TREND REPORT

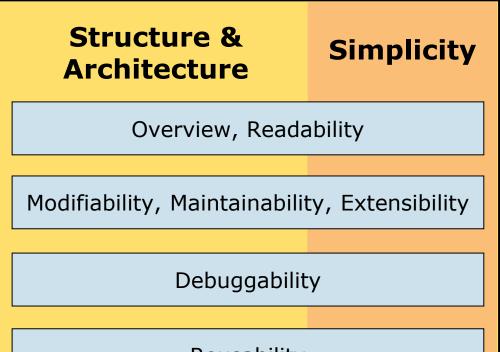

| Structure &<br>Architecture                   | Simplicity |  |

|-----------------------------------------------|------------|--|

| Overview, Readability                         |            |  |

| Modifiability, Maintainability, Extensibility |            |  |

| Debuggability                                 |            |  |

| Reusability                                   |            |  |

### Significantly affects:

- Man hours / Cost

- Schedule & TTM

- Quality & MTTF

- Product LCC

- ... Next project

Easily save 100-500 hours Sometimes 1000-3000 hours

Reduce late project iterations

Faster SW development

More happy customers

## UVVM The main benefits of the world's #1 VHDL Verification Methodology

By Espen Tallaksen, Director FPGA and Space, EmLogic

## EmLogic

The Norwegian Embedded Systems & FPGA Design Centre