## UVVM - Brand new features from the world's #1 VHDL Verification Methodology

FPGA Verification Day, Live Online, 23 September 2021

EmLogic.no

The Norwegian Embedded Systems and FPGA Design Centre

- Independent Design Centre for Embedded Systems and FPGA

- Established 1<sup>st</sup> of January 2021. Extreme ramp up

- January: 1 person

- September:  $\rightarrow$  18 designers (SW:7, HW:1, FPGA:10) **And still growing...**

- Continues the legacy from

- All previous Bitvis technical managers are now in EmLogic

- Verification IP and Methodology provider  $\bigcup \bigvee \bigvee M$

- Course provider within FPGA Design and Verification

- Accelerating FPGA Design (Architecture, Clocking, Timing, Coding, Quality, Design for Reuse, ...)

- Advanced VHDL Verification Made simple (Modern efficient verification using UVVM)

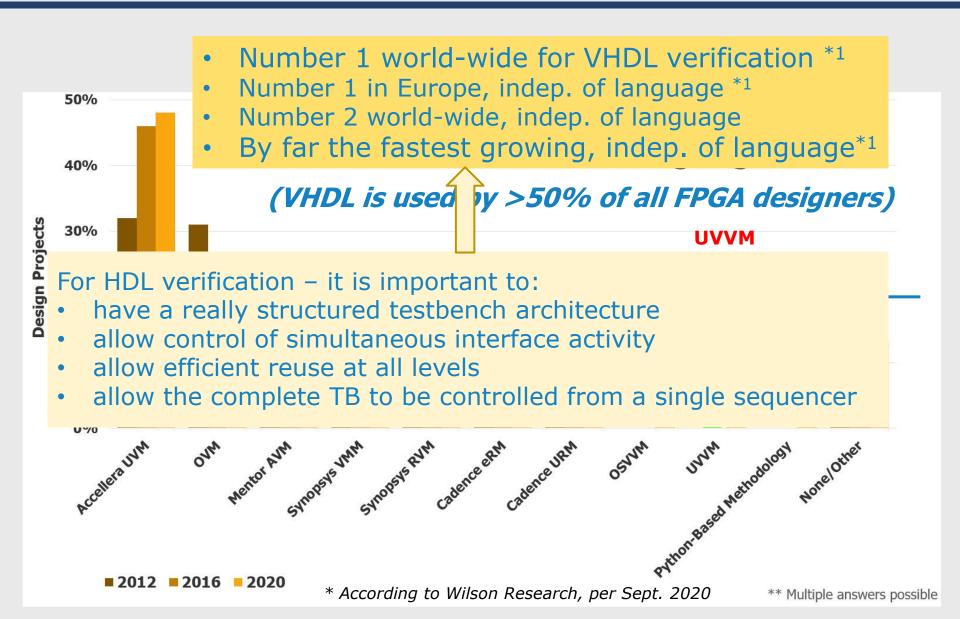

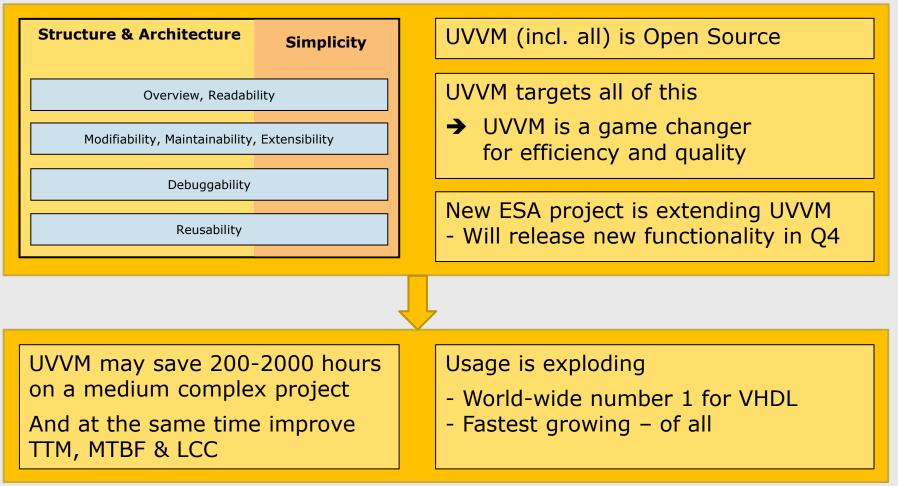

### UVVM – World-wide #1

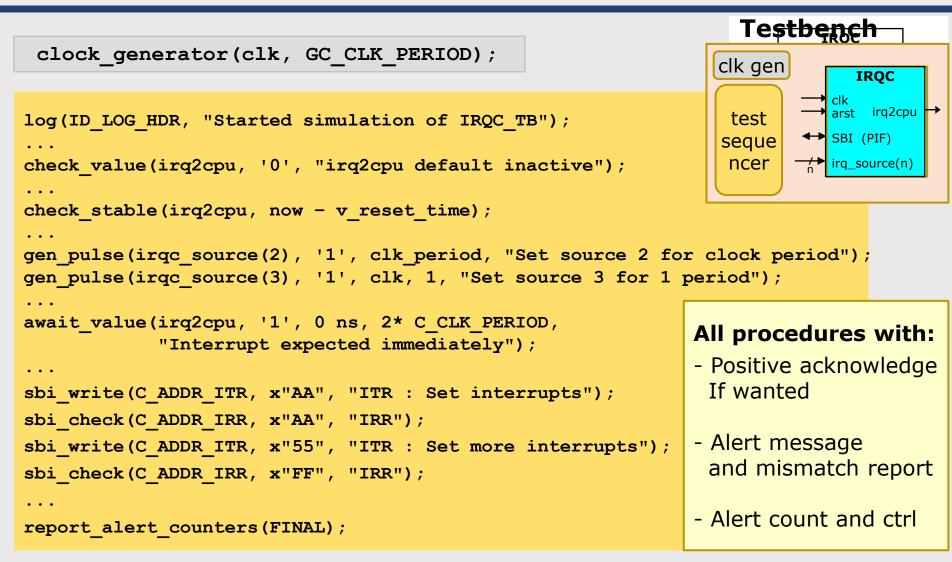

#### Typical simple verif. scenario - a low complexity interrupt controller

## Lot's of free UVVM BFMs and VVCs

- AXI4-lite

- AXI4 Full

- AXI-Stream Master + Slave

- UART Transmit and Receive

- SBI

- SPI Master and Slave

- I2C Master and Slave

- GPIO

- Avalon MM

- Avalon Stream Master and Slave

- RGMII Transmit and Receive

- GMII Transmit and Receive

- Ethernet Transmit and Receive

- Wishbone

- Clock Generator

- Error Injector

#### All:

- Free

- Open Source

- Well documented

- Example Testbenches

The largest collection of Free & Open Source VHDL Interface Models

#### VVC: VHDL Verif. Comps.

- Includes the BFM Allows:

- Simultaneous interface handling

- Synchronization of interfaces

- Skewing between interfaces

- Additional protocol checkers

- Local sequencers

- Activity detection

- Simple reuse between projects

### The newer stuff

- ESA Extensions in ESA-UVVM-1

- Scoreboarding

- Monitors

- Controlling randomisation and functional coverage

- Error injection (Brute force and Protocol aware)

- Local sequencers

- Controlling property checkers

- Watchdog (Simple and Activity based)

- Transaction info

- Hierarchical VVCs And Scoreboards for these

- **Specification Coverage** (Requirement/test coverage)

In addition lots of general improvement have been made

### Today: Focus on New Features

- For an introduction to current functionality like:

- More key functionality in Utility Library

- BFMs : Functionality and usage

- VVC and their benefits

- The new functionality over the last 2 years

- Why UVVM is #1

Check out my previous Webinars, Posts, and Presentations

The latest presentations being:

#### **MODERN VHDL TESTBENCHES**

AN AXI-STREAM EXAMPLE, FIRST dead simple, - THEN advanced - Both as simple as possible

At FPGA Conference Europe, 6 July 2021. (Get in touch if you can't get it there)

#### UVVM

#### The main benefits of the world's #1 VHDL Verification Methodology

At Mentor/Siemens Verification Webinar Series, 4 May 2021 Complete presentation (webinar) available here: <u>https://webinars.sw.siemens.com/uvvm-the-main-benefits-of-the/room</u>

## Brand New 1 - October 2021

- UVVM has had basic Randomisation since 2015

- Good enough for most designers and verification engineers but....

- We have got many requests for:

- More advanced Randomisation in UVVM

- Better integrated verification than current alternatives

- More understandable randomisation APIs

- UVVM now meets these requests with brand new:

- Enhanced Randomisation

- Optimised Randomisation

### Basic Randomisation in "old" UVVM

- Under UVVM Utility library : methods\_pkg

- Simple functions using shared variable seeds:

- my\_int := random(VOID);

- my\_int := random(4, 245);

- my\_slv8 := random(8);

- my\_byte\_array := random(1, 16);

- my\_time := random(1 ns, 15 ns);

- Also provides support for fixed random sequence

- Needs to control seeds locally

- random(4, 245, seed1, seed2, my\_int);

Still the simplest solution for simple Randomisation

### **Enhanced Randomisation**

- Located under UVVM Utility library : rand\_pkg

- New package included in context file

→ Will be available automatically once released

- Uses protected types

variable my\_addr : t\_rand; -- The only preparation reqd.

- Allows far better control of randomisation when needed

- Combine ranges and set of values

- Exclude set of values

- Dedicated control of: 'with replacement' vs 'without replacement'

- Additional multi-method approach for even more detailed control

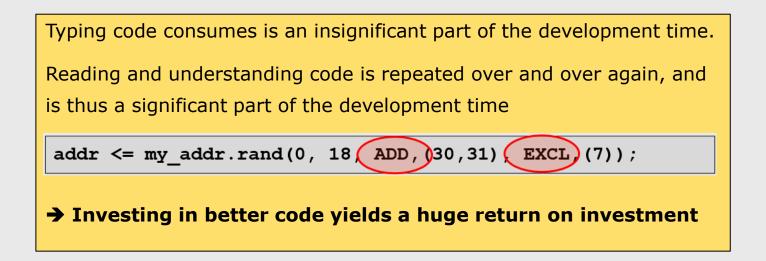

## Single Method approach

#### "Standard" approach: Randomisation in one single command

Simple randomisation is always easy to understand

addr <= my\_addr.rand(0, 18);</pre>

More complex randomisation is normally more difficult to understand BUT – there are ways to significantly improve this

Similar readability focus for weighting

addr <= my\_addr.rand\_val\_weight((0,2),(1,3),(2,5)); addr <= my\_addr.rand\_range\_weight((0,18,4),(19,31,1));</pre>

EmLogic

11

## **UVVM Enhanced Randomisation**

- Well integrated with UVVM

- Alert handling and logging in particular

- Strong focus on Overview & Readability

- Adding keywords to ease understanding

- Easy to Maintain and Extend

#### **Quality & Efficiency enablers**

| Structure & Architecture                      | Simplicity |  |  |  |

|-----------------------------------------------|------------|--|--|--|

| Overview, Readability                         |            |  |  |  |

| Modifiability, Maintainability, Extensibility |            |  |  |  |

| Debuggability                                 |            |  |  |  |

| Reusability                                   |            |  |  |  |

### Other features

#### General Initialisation

| <pre>.set_rand_seeds(string integers)</pre> | ۴ | .get_rand_seeds() |

|---------------------------------------------|---|-------------------|

| <pre>.set_name("address generator")</pre>   | & | .get_name()       |

| .set_scope("UART TX")                       | ٤ | .get_scope()      |

- General functionality configuration

- Randomisation Distribution + Characteristics (Std. Deviation)

- Weighting of ranges vs sets

- Special features

- Unique values in vectors (64 values with unique values between 0 and 255)

```

payload <= my_data_vector.rand(64, 0,255, UNIQUE);</pre>

```

No repeating until all values have been used

addr <= my addr.rand(0, 18, EXCL,(7), CYCLIC);</pre>

## Multi-method approach (1)

- Extends the functionality of the single method approach

- Single method approach:

```

addr_1 <= my_addr.rand(0, 18, ADD,(30,31), EXCL,(7));

addr_2 <= my_addr.rand(0, 18, ADD,(30,31), EXCL,(7));</pre>

```

Multi-method - equivalent

```

my_addr.add_range(0, 18);

my_addr.add_val((30,31));

my_addr.excl_val((7));

addr_1 <= my_addr.randm(VOID);

addr_2 <= my_addr.randm(VOID);</pre>

```

Note: rand**m**() (For clarity and to avoid any ambiguity)

Allows adding more ranges, sets or exclusions

```

my_addr.add_range(48,63);

my_addr.add_range(80,127);

```

• Allows simple inclusion of future extensions

## Multi-method approach (2)

- Slightly more object oriented

- Thus allows simpler build-up multiple constraints

Multi-method approach is better for:

- Reuse of constraints if needed

- More partial or complex constraints if needed

- Modification of constraints if needed

- Future functionality extensions (UVVM or other)

Single-method approach is better if :

- Simple constraints, AND

- No need for future extensions in your current testbenches

One approach does not affect the other, But would not recommend to mix in the same testbench.

### May report configuration

my\_addr.report\_config(VOID);

| *** | REPORT OF RANDOM ( | GEI    | NERATOR CONFIGUE |

|-----|--------------------|--------|------------------|

| === | NAME               | :==    | MY ADDR          |

|     | SCOPE              | :      | <br>AXI4 Master  |

|     | SEED 1             | :      | 1969513907       |

|     | SEED 2             | :      | 1510976018       |

|     | DISTRIBUTION       | :      | UNIFORM          |

|     | WEIGHT MODE        | 0<br>0 | COMBINED_WEIGHT  |

|     | MEAN CONFIGURED    | 0<br>0 | false            |

|     | MEAN               | •      | 0.00             |

|     | STD_DEV CONFIGURED | 0<br>0 | false            |

|     | STD DEV            |        | 0.00             |

## Brand New 2 - October 2021

- UVVM introduced Specification Coverage in 2020

- A huge improvement for the whole VHDL Community

- Allowed the simplest possible way of tracking Requirements

- A boost for any design where Quality is important

- But We have also got lots of requests for:

- More Coverage functionality in UVVM

- Better integrated verification than current alternatives in SV and VHDL

- More understandable expressions and usage

- As a result UVVM is now releasing Functional Coverage

- Based on functional coverage in SV

- But in VHDL, and without all the complexity of SV and UVM

- Fully integrated with UVVM, but may be used stand-alone

# Functional Coverage – X-B-I

- Functional Coverage 'is a user-defined metric that measures how much of the design specification has been exercised in verification'

- Has various functional scenarios been tested.

- A manual process is required to set up all wanted scenarios

- E.g. In a system with a FIFO:

- Has the FIFO been full, and empty

- Has a write been attempted when full (or read when empty)

- Has the FIFO been full followed by read then write

- etc.

- E.g. For a packet oriented protocol (0-256 bytes):

- Has payload size been 0,1,255,256 and something in between

- Has various destination addresses been tested

- Has selected combinations of these been tested

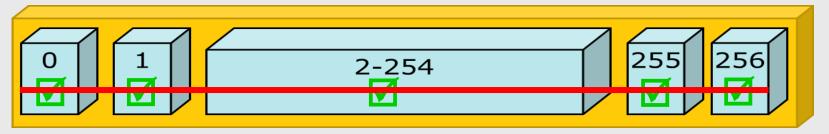

### Define Coverpoints (1) (Things you want to check)

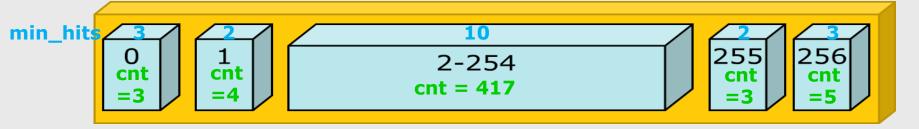

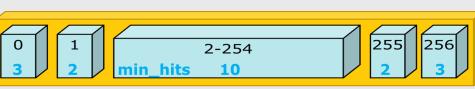

- For the given protocol example: Make sure that corner case payload sizes have been verified

- E.g. at least once for each of: 0, 1, 255, 256 and 2-254

#### A cover point 🗲 🛛 An actual issue to check

The selected values and ranges are called Bins

- Then if you generate a packet with payload size of 1 byte,

→ tick off that value

- Continue making packets of different payload-sizes until all values and ranges have been ticked off.

- → You have now covered all your selected values and ranges

- ➔ Your Payload-size Coverpoint is covered

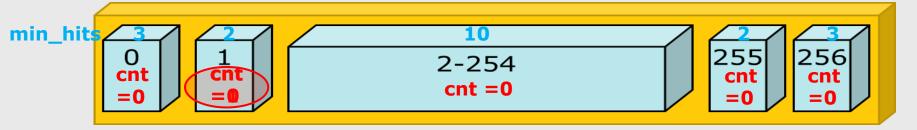

## Define Coverpoints (2) (Things you want to check)

- For the protocol example: Make sure that corner case payload sizes have been verified

- E.g. a minimum number of times for each of: 0, 1, 255, 256 and 2-254

This minimum required number of hits is called min\_hits

- Then if you generate a packet with payload size of 1 byte,

→ Increase the counter for that bin

- Continue making packets of different payload-sizes until all values and ranges have been applied the minimum number of times required

### Define Coverpoints (2) (Things you want to check)

- For the protocol example: Make sure that corner case payload sizes have been verified

- E.g. a minimum number of times for each of: 0, 1, 255, 256 and 2-254

This minimum required number of hits is called min\_hits

- Then if you generate a packet with payload size of 1 byte,

→ Increase the counter for that bin

- Continue making packets of different payload-sizes until all values and ranges have been applied the minimum number of times required.

- → You have now covered all your selected values and ranges

- ➔ Your Payload-size Coverpoint is covered

#### Functional Coverage – Typical Sequence

Define a variable of type t\_coverpoint

```

variable cp_payload_size : t_coverpoint;

```

Add the bins

```

cp_payload_size.add_bins(bin(0));

cp_payload_size.add_bins(bin(1));

cp_payload_size.add_bins(bin_range(2,254,1));

cp_payload_size.add_bins(bin(255,256,2));

```

Tick off bins as their corresponding payload size is used

```

cp_payload_size.sample_coverage(payload_size);

```

Continue sending packets until coverage target is reached

while not cp\_payload\_size.coverage\_completed(VOID);

## Bin generation

| bin(0)                                | single bin for single value          |

|---------------------------------------|--------------------------------------|

| bin((2,3,6,8))                        | single bin for a set of values       |

| <pre>bin_range(0,5)</pre>             | single bin for each value in a range |

| <pre>bin range(0,5,2)</pre>           | two bins split evenly on range       |

| bin vector (addr)                     | 2**addr bins                         |

| bin_vector(addr,16)                   | 16 bins                              |

|                                       |                                      |

| <pre>bin_transition((2,4,8))</pre>    | single bin for given sequence        |

| ignore bin(7)                         | value to be ignored                  |

|                                       | -                                    |

| <pre>ignore_bin_range(5,7)</pre>      |                                      |

| <pre>ignore_bin_transition(4,8)</pre> | sequence to be ignored               |

|                                       |                                      |

| illegal_bin(7)                        | illegal value                        |

| <pre>illegal_bin_range(5,7)</pre>     | illegal range                        |

illegal\_bin\_transition(4,7) -- illegal sequence

### Other Functional coverage features

- .add\_cross() : Cross coverage for two or more crosses

- .is\_defined() : To check if bins have been defined

- Coverage goal modification

- Specific cover point coverage modification (for bins)

- or Overall simulation coverage (for all Coverpoint)

- or both

- Configuration

- Bin name and scope

- Alert settings (Illegal bin, Bin overlap)

- Coverage weight : Weight of CP for overall coverage

- Coverage data base: For accumulation of coverage

#### Some reports – out of many

| # UVVM:            |        |                    |                   |                |              |           |                |                       |     |

|--------------------|--------|--------------------|-------------------|----------------|--------------|-----------|----------------|-----------------------|-----|

| # UVVM:            |        | *** COVERAGE SUMMA |                   |                |              |           |                |                       |     |

| # UVVM:            |        |                    |                   |                |              |           |                |                       |     |

| # UVVM:            | Cover  |                    | Covpt_1           |                |              |           |                |                       |     |

| # UVVM:            | Covera | age (for goal 100) | : Bins: 60.00%,   | Hits: 76.47%   |              |           |                |                       |     |

| # UVVM:<br># UVVM: |        | BINS               | нітя              | MIN HITS       | HIT COVERAGE |           | NAME           |                       |     |

|                    |        |                    |                   |                |              | 4.1.1     |                | ILLEGAL/IGNORE        |     |

| # UVVM:            |        | (256 to 511)       | 1                 | N/A            | N/A          |           | egal_addr      | ILLEGAL               |     |

| # UVVM:            |        | (0 to 125)         | 6                 | 8              | 75.00%       |           | _addr_low      | -                     |     |

| # UVVM:            |        | (126, 127, 128)    |                   | 1              | 100.00%      |           | _addr_mid      | -                     |     |

| # UVVM:            |        | (129 to 255)       | 14                | 4              | 100.00%      |           | _addr_high     | -                     |     |

| # UVVM:            |        | (0->1->2->3)       | 0                 | 2              | 0.00%        |           | nsition_1      | -                     |     |

| # UVVM:            |        | transition_2       | 2                 | 2              | 100.00%      | tra       | nsition_2      | -                     |     |

| # UVVM:            |        |                    |                   |                |              |           |                |                       |     |

| # UVVM:            | trans: | ition_2: (0->15->1 | 27->248->249->250 | )->251->252->2 | 53->254)     |           |                |                       |     |

| # UVVM:            |        |                    |                   |                |              |           |                |                       |     |

| #                  | UVVM:  |                    |                   |                |              |           |                |                       | ==  |

| #                  | UVVM:  | 0 ns *** OVERALL   | COVERAGE REPORT ( | VERBOSE): TB s | ea. ***      |           |                |                       |     |

| #                  | UVVM:  | Coverage (for goal | 1 100): Covpts: 5 | 0.00%, Bins:   | 73.68%, Hit  | s: 76.00% |                |                       |     |

| #                  | UVVM:  |                    |                   |                |              |           |                |                       | ==  |

| #                  | UVVM:  | COVERPOINT         | COVERAGE WEIGHT   | COVERED BINS   | COVERAGE (B  | INS HITS) | GOAL(BINS HITS | ) % OF GOAL(BINS HITS | )   |

| #                  | UVVM:  | Covpt_1            | 1                 | 3 / 5          | 60.00%       | 76.47%    | 50%   100%     | 100.00%   76.47%      |     |

| #                  | UVVM:  | Covpt_2            | 1                 | 3/3            | 100.00%      | 100.00%   | 100%   100%    | 100.00%   100.00%     | i i |

| #                  | UVVM:  | Covpt_3            | 1                 | 6 / 6          | 100.00%      | 100.00%   | 100%   100%    | 100.00%   100.00%     | 5   |

| #                  | UVVM:  | Covpt_4            | 1                 | 0/4            | 0.00%        | 0.00%     | 100%   100%    | 0.00%   0.00%         |     |

| #                  | UVVM:  | Covpt_5            | 1                 | 0 / 1          | 0.00%        | 0.00%     | 100%   100%    | 0.00%   0.00%         |     |

| #                  | UVVM:  | Covpt_6            | 1                 | 4 / 4          | 100.00%      | 100.00%   | 100%   100%    | 100.00%   100.00%     | 5   |

| #                  | UVVM:  | Covpt_7            | 1                 | 0/3            | 0.00%        | 0.00%     | 100%   100%    | 0.00% 0.00%           |     |

| #                  | UVVM:  | Covpt_8            | 1                 | 12 / 12        | 100.00%      | 100.00%   | 100%   100%    | 100.00%   100.00%     | 5   |

|                    | UVVM:  |                    |                   |                |              |           |                |                       | ==  |

25 UVVM - Brand new features ...

## **Optimised randomisation**

- Optimised Randomisation is

- Randomisation without replacement

- Weighted according to target distribution AND previous events

- Uses Functional Coverage mechanisms and protected type

- Target = bins with min\_hits

- ightarrow the lowest number of randomisations for a given target

- ➔ Major reduction in # packets and thus simulation time

- Is basically Randomisation and Functional Coverage in one

- Functional need and Use case is Optimised Randomisation

- Mechanism used is that of Functional Coverage + Weight + Rand

B:25%

B:40%

#### Development and Release of Randomisation and Functional Coverage

Developed and maintained by Inventas and EmLogic

- Beta version will be released on Github in October

- As an extension on UVVM utility library

- Active UVVM users may have the Alpha version sooner

- Send request to <a href="mailto:et@emlogic.no">et@emlogic.no</a>

### Also Brand new: UVVM Steering group

- Founding members are Inventas and EmLogic

- We have been cooperating on UVVM since January 2021

- Both on the ESA project and on general UVVM development

- All rights will be given to the UVVM Steering group

- Copyrights, Github repo, UVVM forum, uvvm.org

- Was founded yesterday...

- Steering group Organisation to be defined

- Steering group to be extended ASAP after that

- We welcome members from the Industy, EDA and Academia

- <u>Must</u> have a strong interest in verification functionality for VHDL

- <u>Must</u> have a good knowledge of and experience with UVVM

- **Must** want to make UVVM a great tool for the VHDL community

- → Send email to <a>et@emlogic.no</a> and include reason for wanting to join

## **Design and Verification Courses**

#### Advanced VHDL Verification – Made simple

• Munich 26-28 October (May change to 5-day online. TBD next week)

#### Accellerating FPGA and Digital ASIC Design

• Munich 10-11 November (May change to 3- or 4-day online. TBD soon.)

#### More courses on demand/request

- On-site, online, public. In Europe and outside Europe

- May adapt or combine courses to your needs

| <u>Design</u>                                                                                                                                                                                                                                                                  | <u>Verification</u>                                                                                                                                                                                                                                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Design Architecture &amp; Structure</li> <li>Clock Domain Crossing</li> <li>Coding and General Digital Design</li> <li>Reuse and Design for Reuse</li> <li>Timing Closure</li> <li>Quality Assurance - at the right level</li> <li>Faster and safer design</li> </ul> | <ul> <li>Verification Architecture &amp; Structure</li> <li>Self checking testbenches</li> <li>BFMs – How to use and make</li> <li>Checking values, time aspects, etc</li> <li>Verification components</li> <li>Advanced Verif: Scoreboard, Models, etc</li> <li>State-of-the-art verification methodology</li> </ul> |

| https://emlogic.no/courses/                                                                                                                                                                                                                                                    | - Also includes UVVM CR and FC usage                                                                                                                                                                                                                                                                                  |

29

## UVVM in a nutshell

Huge improvement potential for more structured FPGA verification

# Thanks for your attention

Community contributions to UVVM are very welcome... Please let me know if this would be possible et@emlogic.no

The Norwegian Embedded Systems and FPGA Design Centre